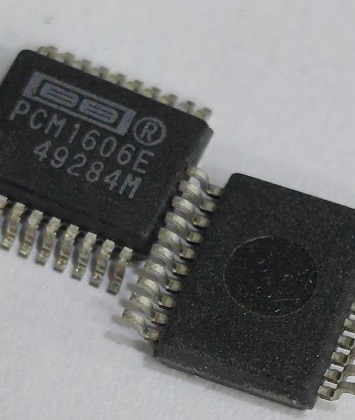

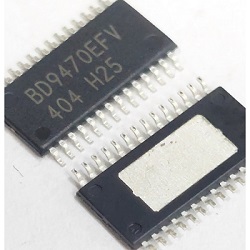

PCM1606E SSOP-20

آیسی PCM1606E یک مبدل دیجیتال به آنالوگ (DAC) صوتی ۲۴ بیتی و ۶ کاناله از شرکت Texas Instruments است که در بستهبندی SSOP-20 عرضه میشود. این تراشه برای کاربردهای صوتی با کیفیت بالا طراحی شده و از معماری Delta-Sigma با چند سطح پیشرفته بهره میبرد.

125,000 تومان

20 در انبار

-

Official retailer

-

Quality guaranteed

-

Free delivery from $99

-

Free returns is available

توضیحات

مشخصات کلیدی

-

وضوح (Resolution): ۲۴ بیت

-

تعداد کانالها: ۶ خروجی آنالوگ مستقل

-

نرخ نمونهبرداری (Sampling Rate): تا ۱۹۲ کیلوهرتز

-

نسبت سیگنال به نویز (SNR): ۱۰۳ دسیبل

-

رابط داده دیجیتال: I²S (استاندارد صنعتی برای انتقال دادههای صوتی دیجیتال)

-

ولتاژ تغذیه: ۵ ولت

-

بستهبندی: SSOP-20 (سطحنصب)

-

دمای کاری: از -۲۵ تا +۸۵ درجه سانتیگراد

کاربردها

-

سیستمهای صوتی چندکاناله (مانند گیرندههای AV و سینمای خانگی)

-

تلویزیونهای دیجیتال و پخشکنندههای DVD

-

کارتهای صدای حرفهای و تجهیزات استودیویی

-

سیستمهای صوتی خودرو

-

تجهیزات پخش و ضبط صدا با کیفیت بالا

توضیحات تکمیلی

| Package |

TSSOP20 |

|---|---|

| کیفیت |

original |

برای ثبت نقد و بررسی وارد حساب کاربری خود شوید.

دیدگاهها

پاکسازی فیلترهیچ دیدگاهی برای این محصول نوشته نشده است.